- HOW TO PROGRAM A LATTICE CPLD PROGRAMMER SERIAL NUMBER

- HOW TO PROGRAM A LATTICE CPLD PROGRAMMER DRIVER

- HOW TO PROGRAM A LATTICE CPLD PROGRAMMER SOFTWARE

HOW TO PROGRAM A LATTICE CPLD PROGRAMMER SERIAL NUMBER

This requires using the TE0790 cable, and if you have the Arrow cable plugged in at the same time, you might need to run fpgajtag with the -s option to specify the serial number of the cable to uses. Second step is to program the Xilinx FPGA, because our current MAX10 firmware connects the JTAG interface to the Xilinx FPGA until it asserts the FPGA_DONE signal, i.e., has been programmed.

HOW TO PROGRAM A LATTICE CPLD PROGRAMMER DRIVER

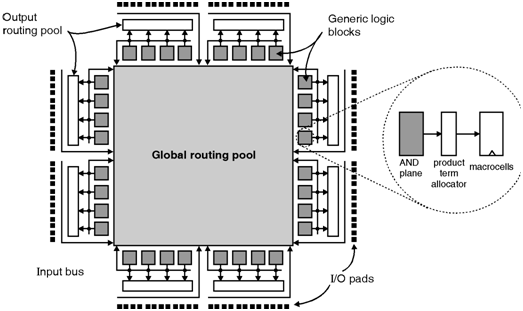

Then the normal Quartus programmer interface can be used (but remember to first have fixed the problem with the Arrow FTDI USB driver setup by following these instructions).Īctually, we simplified this by making a program.sh script, that does the programming itself - but you still have to hold the reset button in. The Arrow FPGA programmer module needs to be plugged in to do this. This done using the Quartus tools, but remember to hold the reset button in on the MEGA65 mainboard, as that asserts the JTAGEN line on the MAX10. That just leaves the Lattice FPGA in the keyboard to program.įirst step is to program the MAX10, so that can route the JTAG to the Xilinx and Lattice FPGAs. Readmore ››Okay, so we have the main Xilinx FPGA and the utility Altera MAX10 FPGA able to be programmed on the MEGA65 R2 mainboard now. These definitions explain the main difference between CPLD and FPGA. The first is by using a macro command file with DebugJet target server application to specify the jedec file and the functions to be executed on the programmable logic device.ĬPLD is an integrated circuit that helps to implement digital systems whereas FPGA is an integrated circuit designed to be configured by a customer or a designer after manufacturing. There are two ways to program a CPLD/FPGA device using DebugJet JTAG interface.

As seen in the MachXO™ Mini Development Kit User’s Guide EB41 schematics, the PB0, PB2, PB3 and PD2 are used for TCK, TMS, TDI and TDO respectively. The EEPROM need to be programmed with C圜onsole after installing the Cypress SuiteUSB. The VID and PID can be got from the driver files that came with the Lattice programming software. We need to program the correct VID and PID of the Lattice USB ISP Programmer. The design is “fit” to a particular CPLD, providing the physical aspects such as resource utilization and timing. The design is simulated for functional correctness.

HOW TO PROGRAM A LATTICE CPLD PROGRAMMER SOFTWARE

The design is written in a high-level language, such as Verilog or VHDL, using a software development tool. A simplified description of CPLD design flow is as follows: 1.

0 kommentar(er)

0 kommentar(er)